近日,殷鹏团队联合西安电子科技大学集成电路学院,在高速串行通信接口领域取得新进展;相关研究成果以题为“A Low-Latency Synchronization Header Detector and Hardware-Efficient Correction Decoder for JESD204C Receiver”的论文被国际集成电路领域顶级期刊《IEEE Transactions on Circuits and Systems I: Regular Papers》接收发表。h漫画

殷鹏为第一作者,西安电子科技大学集成电路学院舒洲教授为通讯作者,h漫画

为论文第一单位和通讯单位。

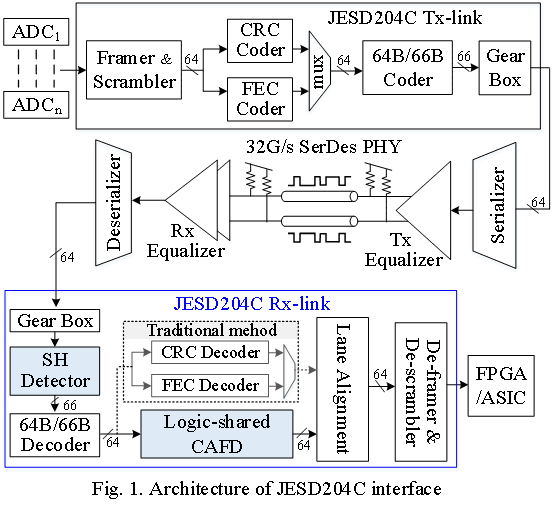

5G通信网络蓬勃发展的今天,5G对应的基础设施需要具有更大带宽,以达到更快的处理速度。高速通信接口JESD204C是数据转换器和逻辑设备之间的主流接口,满足高带宽、高传输效率和高鲁棒性的应用需求。但是,JESD204C存在链路初始化时间长、硬件面积大及功耗高等局限性。研究团队提出基于动态搜索空间、逻辑共享架构和关键路径识别算法的链路层优化设计,提升数据检测的效率与可靠性,并缩减解码电路的硬件开销。验证结果表明,本设计能够加速链路初始化与同步过程并提升硬件资源利用率,为高速数据转换系统提供了高能效、低延迟的解决方案。

论文信息 DOI:10.1109/TCSI.2026.3662461